CIS制造工艺探秘:从FSI到BSI,再到堆栈式方案的演进

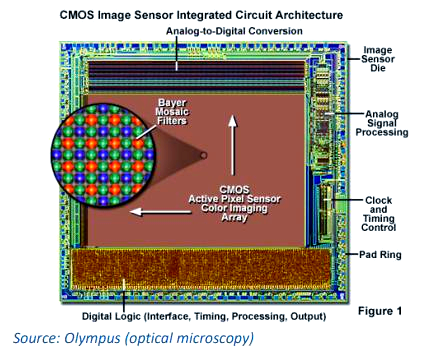

CIS(CMOS Image Sensor),作为摄像头模组的核心,是一种将光信号转化为电信号的光学传感器。其工作机制可概括为:光线经镜头汇聚至传感器后,由感光单元阵列捕捉拍摄对象的亮度与色彩信息,进而将这些光信号转换为电信号。随后,模数转换模块将电信号转化为数字信号,并经过预处理后输出。

深入CIS结构,我们会发现其关键模块包括像素阵列、时序控制器、模拟信号处理器以及模数转换器等。这些模块的精密制造工艺,直接决定了CIS的性能与品质。

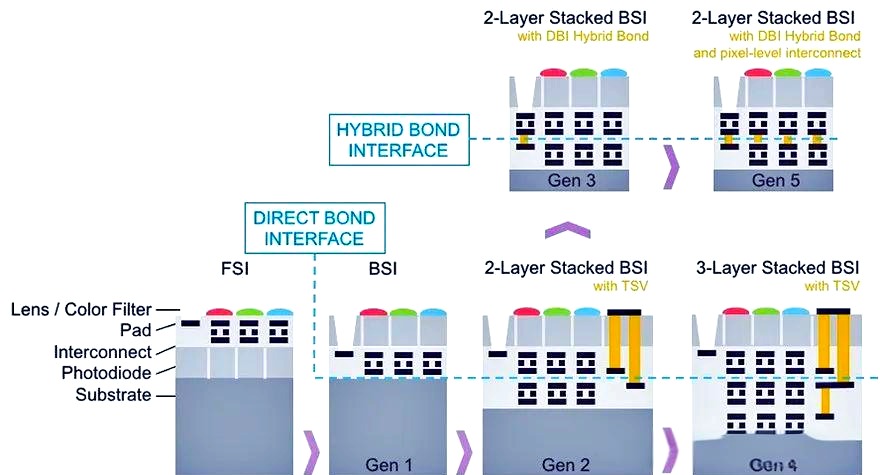

依据像素单元与逻辑单元的相对布局及其制造工艺,CIS的结构主要可分为前照式FSI、背照式BSI以及堆栈式Stacked三种类型。

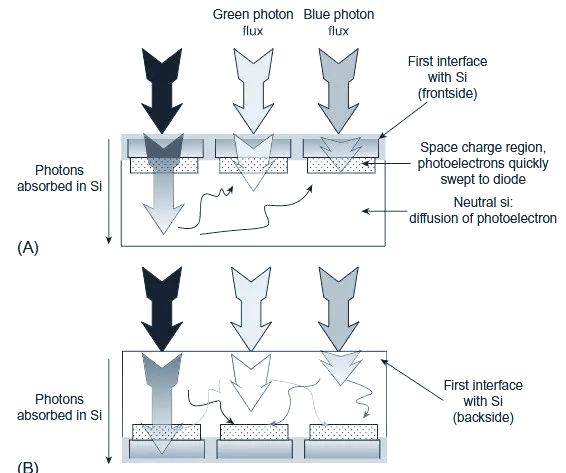

在FSI结构中,金属层位于光电二极管(PD)之上,这会导致感光路径受到金属线的干扰,进而影响感光效率。

相比之下,BSI结构则将金属层布置在PD的下方,有效减少了金属线对感光路径的干扰,从而提高了感光效率。

而堆栈式Stacked结构则更进一步,通过像素层与逻辑层的垂直互联,不仅增大了感光面积,还显著提升了成像效果。

1. FSI CIS的结构特点

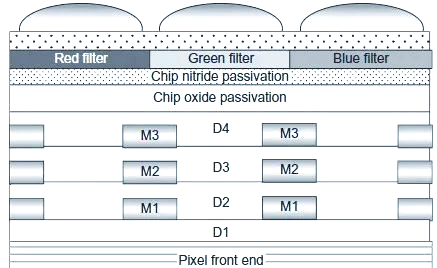

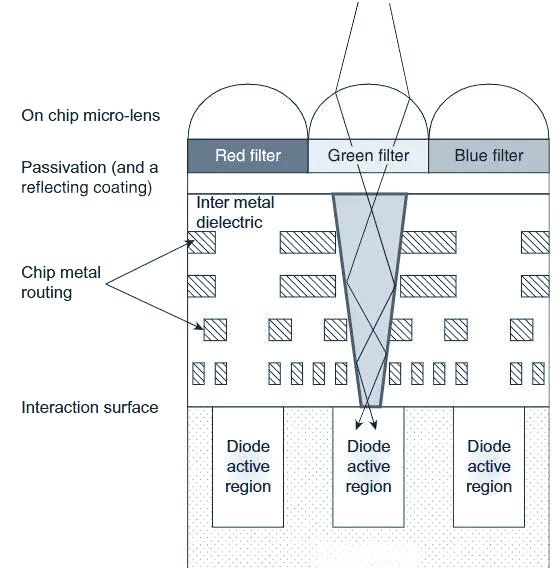

FSI CIS的结构大致如下:像素区域采用三层金属布线,而逻辑区域则使用四层金属。钝化层由氧化物和氮化硅组成,其上覆盖着红色、绿色和蓝色的滤光片,再上方则安置了微透镜。当光线进入硅基底之前,它必须穿过厚厚的金属层,这会导致光子损失。这种损失主要由以下几个机制造成:钝化层的光反射,PD周边金属线的光反射,以及光线偏移和大角度入射,特别是在边缘区域,光线可能被相邻像素收集,从而降低了量子效率(QE),进而影响了传感器的信噪比。

FSI CIS面临的问题及相应解决方案:

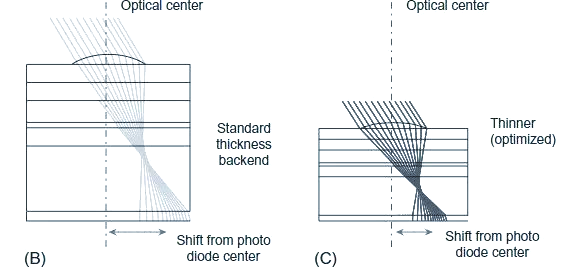

(1)光线到达PD的路径过长时,容易进入邻近像素,导致严重的crosstalk。传统的应对策略是增强micro-lens的聚光能力并降低BEOL的整体高度。当micro-lens更接近PD时,能够捕获的有效光子数量会相应增加。如以下图示(B)和(C)所示,与厚BEOL相比,在较薄的BEOL上安置微透镜,可使光线更精准地聚焦在PD中心附近。

(2)通过减少pixel区域的metal层数至两层,同时保持logic区域为四层金属,我们可以优化工艺流程。在完成四层金属工艺后,对pixel区域进行recess处理,随后在第二层金属上方进行color filter和micro-lens的加工。这种改变传统加工顺序的方法,不仅缩短了光线路径,还显著提升了像素性能,特别是对于倾斜光线的处理。

(3)针对光线进入最上层金属时的孔径问题,我们采取了加大PD上方光学开口的措施。这通常通过使用更窄的控制线来实现,已成为像素迭代中的关键技术。随着CIS工艺发展到0.13μm,采用铜线替代铝线,使得控制线更窄,从而增大了光学开口。此外,铜线的轻薄特性也有助于降低BEOL总高度。

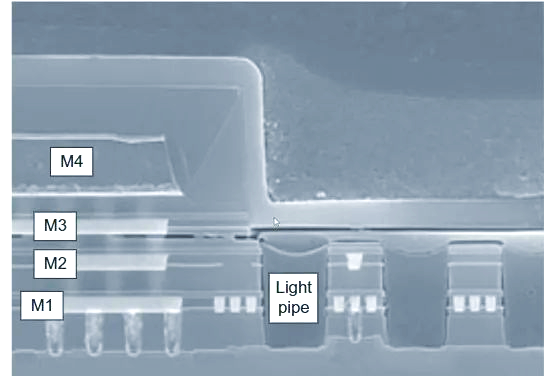

(4)针对铜线介电层中氮化物和氧化物交替导致的光线反射问题,业界提出了光管解决方案。通过蚀刻形成从钝化层到PD表面的深通孔,并旋涂玻璃或高折射率聚合物,将光线约束在光管中,从而降低像素串扰。然而,此方案面临高AR蚀刻、光管深度均匀性、管壁钝化及光管填充等挑战。值得注意的是,不同的pixel pitch需要不同的蚀刻和填充参数,因此在pixel迭代过程中需要不断优化这些参数。

下图中展示的芯片,其制造工艺为65nm铜金属化。在逻辑区域,我们使用了四层金属布局,而在像素区域,则巧妙地采用了两层金属设计。此外,该芯片还融入了光管技术,这一创新举措旨在进一步降低光学串扰的影响。

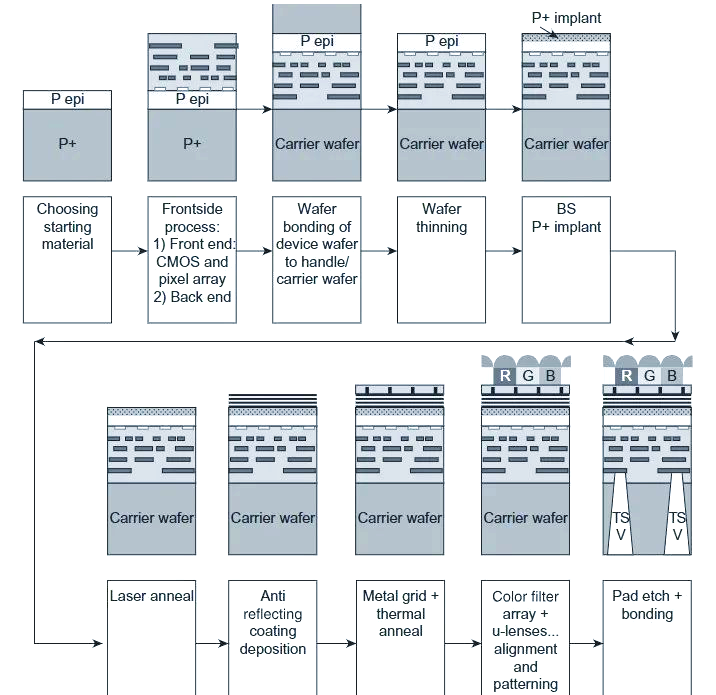

2. BSI CIS

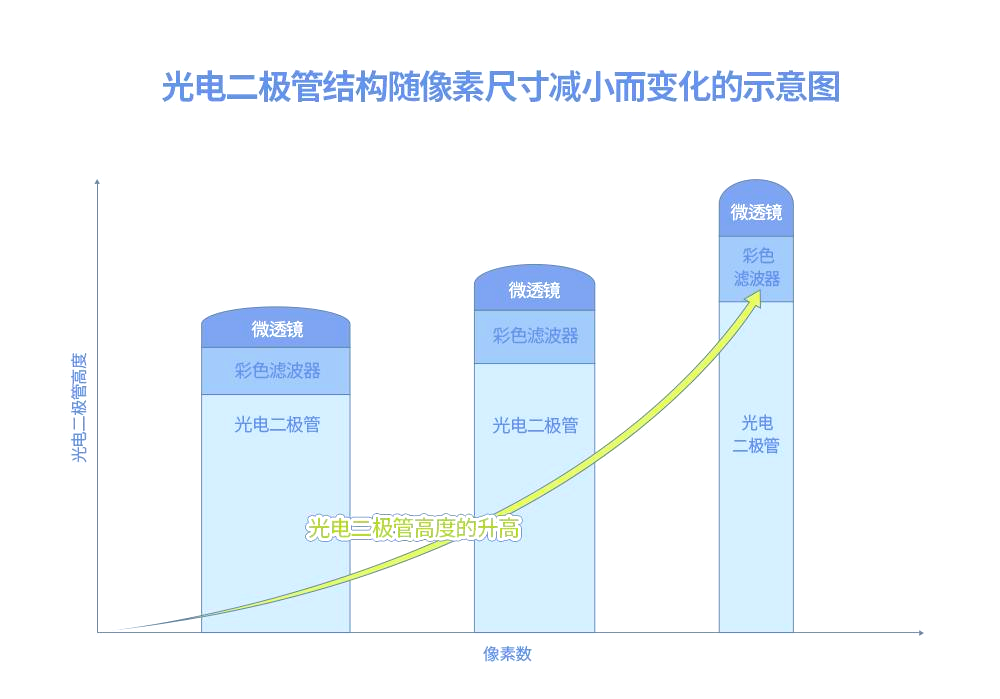

随着像素尺寸的不断缩小,FSI技术中的像素有效感光面积也逐渐缩减。为应对此挑战,行业逐渐转向BSI技术。通常,像素尺寸小于2um的情况更倾向于采用BSI结构。BSI的工艺流程包括:基板制备、前端工艺、后端工艺、晶圆键合、晶圆减薄、表面钝化、自动频率控制、深层阱隔离、高k介质层、金属网格、彩色滤光片以及微透镜制作。由于光线从晶圆背面直接进入二极管,无需穿越金属层,因此小尺寸像素下的量子效率(QE)得到了显著提升。

(1)基板选择

基板类型对BSI工艺有着重要影响。一种常用的是高阻epi wafer,其价格相对亲民,器件制备在epi层,epi厚度大约为6μm,阻值约为10 Ohm-cm,而基板阻值则为0.05 Ohm-cm。另一种则是SOI wafer,其特点是埋氧化层(BOX)可作为减薄的刻蚀停止层,从而实现对减薄厚度的精确控制,但成本相对较高。

BSI的前端工艺与标准CMOS工艺类似,包括一系列复杂的步骤。这些步骤大致如下:AA/STI → Well implant → Pixel implant → Gate Oxide → Poly Gate → OFFSET → LDD → SPACER → S/D → ESD → Salicide → ILD → CT。尽管具体到每个步骤和配方,不同的fab可能会有所差异,但优化的方向和思路是保持一致的。

(3)深层光电二极管技术

在BSI技术中,需要关注的一个问题是串扰。由于绿色和蓝色光子在前0.5μm深度的吸收率存在差异,这可能导致串扰的增加,进而影响单色传感器的调制传递函数(MTF)和彩色插值的信噪比(SNR)。这一技术挑战需要在实际应用中加以考虑和优化。

采用深层光电二极管技术是确保图像质量不受损失的重要手段。通过这项技术,即便在尺寸更小的像素中,也能确保充足的满阱容量,以应对高达800keV甚至超过1MeV的注入能量,从而创造出适宜绿色光电子吸收的深二极管。这一过程需要运用高纵横比的掩膜工艺,确保光刻胶(PR)能够有效阻挡高能离子的注入。

Pixel transistor的设计

Pixel transistor与logic IO device共享相同的电压范围,即2.5~3.3V,但pixel区域必须采用厚氧化物技术。为了优化性能,需要调整Pixel transistor的阈值电压(Vt),以实现最大的摆幅并最小化漏电流。此外,增大栅极长度是必要的,这样可以减少热载流子引发的光子发射和冲击电离效应。

S/D implant的考虑

在某些logic工艺中,S/D implant可能掺杂了Ge。在这种情况下,为了确保pixel区域的纯净性,需要采用专门的pixel S/D implant工艺,以避免Ge掺杂的影响。

Pixel区域的非硅化技术

在pixel区域,我们选择使用non-silicided S/D和poly gate,因为silicide材料会吸收光线,从而降低光敏性。

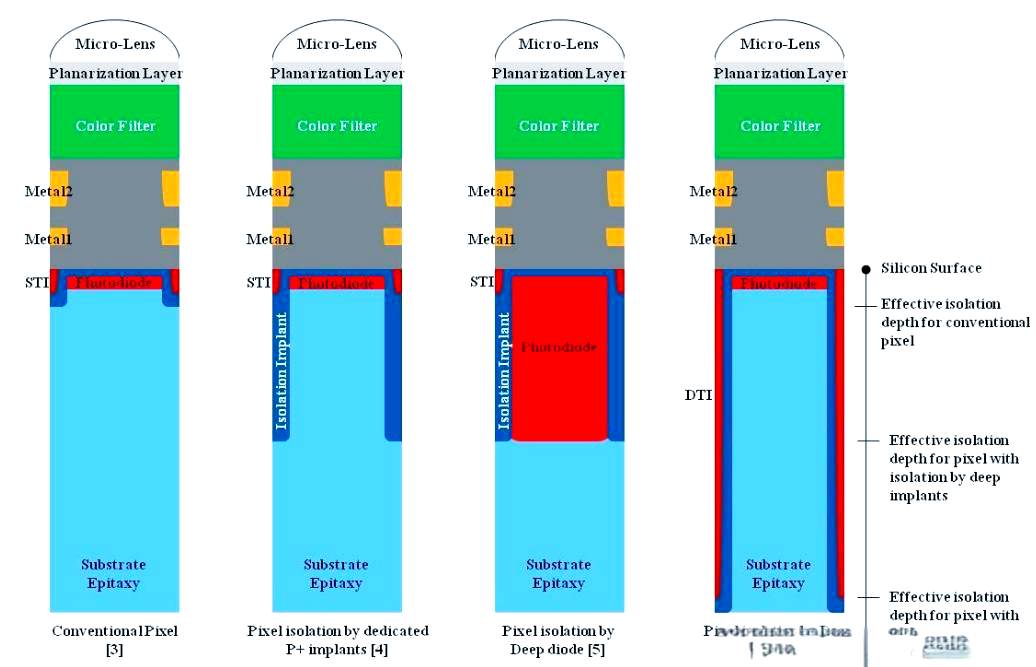

像素间隔离技术

像素隔离是高清CIS中的关键技术,主要采用deep P well和DTI等工艺。不同的芯片制造商可能采用不同的隔离技术,而这些技术的水平直接影响到CIS的品质。因此,隔离处理技术的优劣已成为衡量CIS性能的重要标准。

金属吸附技术

在高清CIS的制造过程中,金属污染是一个不可忽视的问题。这些金属原子会为暗电流提供传输路径,进而影响图像在黑暗环境下的性能。为了解决这一问题,像素隔离技术显得尤为重要。在P型外延片衬底上,氧化层和掺杂多晶硅的存在使得金属原子能够被有效吸附。而对于SOI衬底,由于其特殊的结构,重金属无法穿过埋氧化层,因此需要采用额外的工艺来去除金属元素。

为了进一步优化这一过程,多种金属吸附技术被提出。其中,局域吸附技术通过修改FEOL flow,将吸附中心置于像素区域附近,从而实现对金属原子的有效控制。垂直吸附技术则通过在AA区域或硅衬底上创建吸附中心,打破BOX层,使得金属原子能够顺利移动到衬底并被有效去除。此外,横向吸附技术也被广泛研究,例如将金属原子吸附到深沟槽中,通过特定的工艺流程实现对金属的分离和去除。

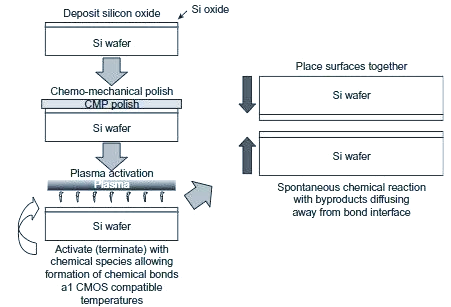

另一方面,BEOL工艺流程与CMOS工艺相似,主要涉及Al线和Cu线两种工艺的选择。而wafer bonding技术则是在后续工艺中提供机械支撑的关键步骤。通过CMP清洁device wafer和carrier wafer的表面,并进行等离子体活化处理,将两个表面面对面放置进行键合,从而确保后续工艺的顺利进行。在direct bonding过程中,对表面特性的严格控制也是必不可少的,以确保键合的强度和可靠性。

(5)晶圆减薄

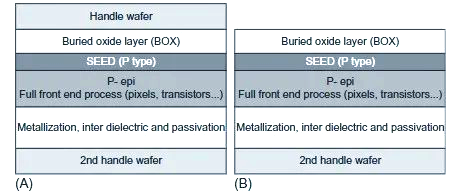

对于SOI衬底,其晶圆减薄工艺相对简单,这恰恰是SOI衬底备受青睐的一个关键因素。具体的减薄流程包括:首先去除硅层,直至达到BOX层,随后再进一步去除BOX层,并最终在Si层上停止。以下是晶圆减薄前后的示意图:

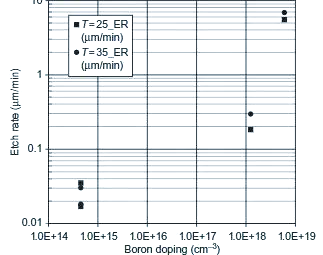

对于P型外延衬底,由于其减薄过程中缺乏蚀刻停止层,使得这一工艺极具挑战性。为了应对这一难题,通常利用P层与P+层之间的浓度差异来作为刻蚀的停止界面。下图展示了氢氟酸-硝酸-乙酸(HNA)溶液的刻蚀速率与掺杂浓度的关系。从图中可以看出,当掺杂水平低于10^18atoms/cm3时,蚀刻速率变得相对缓慢。因此,当P层的掺杂水平约为10^15atoms/cm3,而P+层的掺杂水平则达到10^19atoms/cm3时,晶圆减薄便拥有了足够的余裕。具体的减薄流程如下:首先通过机械研磨的方式,将硅从大约700μm的初始厚度逐步研磨至20μm左右,然后再利用湿法刻蚀技术,将硅进一步减至所需的目标厚度。

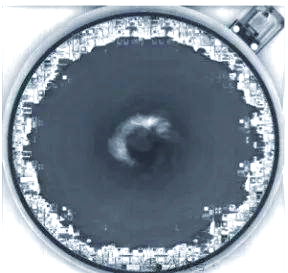

实际上,湿法蚀刻过程中面临诸多挑战。首先,硼元素可能从P+层扩散至P层,导致两者边界在FEOL工艺中的高温退火环节变得模糊。这影响了减薄过程中以边界为蚀刻停止层的可行性。其次,晶圆边缘(包括顶部和侧面)直接暴露于蚀刻液中,使得边缘区域的蚀刻速度超过中心区域。例如,在缺乏边缘保护的情况下,一个200mm晶圆的蚀刻图片显示边缘区域被过度蚀刻。此外,由于PR材料会被HNA蚀刻液去除,且边缘区域的PR去除需要非标准曝光技术,这使得边缘保护变得更为复杂。最后,蚀刻后的表面粗糙度问题需要通过CMP工艺来解决,以确保满足后续工艺的要求。

(6)表面钝化

在FSI工艺中,表面钝化是通过高剂量implant进行表面钉扎,并利用高温退火进行激活来完成的。然而,对于BSI工艺,情况则有所不同。由于晶圆上已存在金属层,这些金属层无法承受高温热循环,因此不能采用FSI工艺中的钝化方法。为此,我们介绍了三种适用于BSI的表面钝化方法。

首先是激光退火。该方法已在BSI生产中广泛使用。它涉及在晶圆背面进行浅P型注入,随后通过激光束脉冲进行退火。由于脉冲持续时间极短(约几百纳秒),因此不会改变金属层区域的温度。然而,该方法也存在一些挑战,如使用成本较高的专用设备、大尺寸CIS退火需要多次激光照射导致图像瑕疵,以及优化注入和退火工艺以获得短波长下的高QE等。

另一种方法是采用低温生长的高掺杂外延层进行钝化。这种方法在BSI CCD和CMOS传感器中得到了广泛应用。其优点是在短波长下能实现高QE,但缺点是需要低温外延生长,并且通常只能通过成本高昂、吞吐量低的分子束外延(MBE)方法生长。

最后一种方法是使用具有负固定电荷的电介质进行钝化。例如,可以采用Al2O3作为钝化层,将其沉积在SiO2上。Al2O3固有的固定负电荷会在Si和SiO2之间的界面附近形成一个移动的空穴积累层,在某些情况下可以起到固定界面的作用。这种方法的优点是工艺简单且与标准工艺兼容,但缺点是在Al2O3层中难以获得大量受控的固定电荷。

(7)深沟槽隔离

深沟槽隔离(DTI)并非必须,但对于小尺寸pixel的隔离至关重要。DTI通常将Si蚀刻至bonding界面。一种常见的实现方案是在DTI内部填充AFC和oxide。另一种方案则是再次蚀刻DTI中的oxide,确保侧壁保留一定厚度的oxide,随后在DTI中填充W,这与BCD中的DTI工艺类似。

(8)抗反射涂层

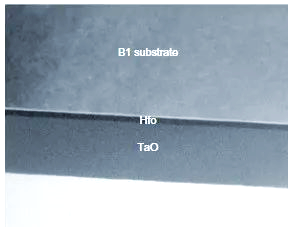

BSI传感器的一大优势在于能够自由应用专为提高QE而设计的抗反射涂层(ARC)。这些常用材料包括HfO2、SiON、SiO2、MgF2以及Ta2O5等,其厚度大约在几十纳米左右。以Sony的1.55μm BSI CIS为例,其上便应用了此类ARC。这种抗反射涂层在光学上能减少光线反射,从而提高光线的利用率;而在电学上,它则能提供负电荷,有助于吸附金属元素并降低暗电流。在填充了AFC之后,会进一步进行oxide的填充,以及深沟槽隔离(DTI)中的DTI ET和W的填充。

(9)金属网格

在每个像素的物理边界处,通过沉积和图案化金属,形成了金属网格。在小尺寸像素中,光线往往会到达像素边缘,这增加了像素间的串扰。为了减少这种光学串扰,我们采用了metal grid来制造电势屏障,从而阻止电子进入相邻像素。这一工艺中,通常使用W作为主要材料。若选择使用DTI,DTI中的W可用于构建metal grid,随后填充oxide并执行CMP工艺。

(10)PAD开放

经过一系列工艺后,最后进行Pad open。这一步骤涉及蚀刻去除PAD上方的Si和介质层,直至露出metal层,例如M1或TM。不同fab的工艺可能有所不同。之后,沉积Al并进行图案化,仅保留PAD上方的Al部分。然后,沉积oxide作为PAS,并进一步图案化PAS,在PAD上方形成开口,为后续封装做准备。

(11)Color filter和micro lens的制作挑战

在制作Color filter和micro lens的过程中,主要面临两大难题:一是光学堆栈与金属网格的精准对准;二是处理减薄后的硅厚度。对于小尺寸CIS,减薄后的硅厚度可能超过2μm,而在高端CIS中,这一厚度甚至可能超过5μm。为了确保对准精度,通常需要借助IR对齐工具。此外,研发人员也在探索新的对齐方案,例如在晶圆正面构建深沟痕,减薄后使其暴露在晶圆背面,从而为背面对齐提供参考。

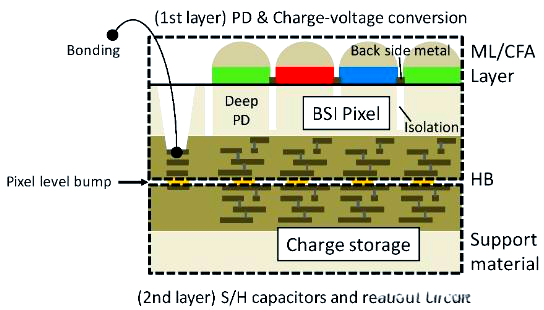

3. 堆栈式CIS技术

由于pixel和logic都位于同一平面上,这在一定程度上限制了pixel的进一步微型化。为了克服这一挑战,堆栈式CIS方案应运而生。该方案将pixel与logic分别制造在独立的晶圆上,随后通过bonding技术将pixel晶圆与logic晶圆相连结,并经过BSI工艺进行处理。为了确保wafer之间的电气互连,行业内主要采用硅通孔TSV技术和Cu-Cu hybrid bonding技术。堆栈式结构不仅提升了pixel的有效感光面积,从而优化了成像效果,还允许pixel晶圆和logic晶圆分别采用不同的工艺节点进行加工,这极大地简化了工艺流程并促进了复杂功能的集成。

4. 像素单元详解

接下来,我们将深入了解感光像素单元的构成。一个完整的像素单元包含微透镜、彩色滤光膜和像素阵列三个关键部分。其中,微透镜和彩色滤光膜作为光学元件,负责收集和过滤光线;而像素阵列,作为电学组件,通过金属层与逻辑处理单元相连结,实现电信号的传输与处理。

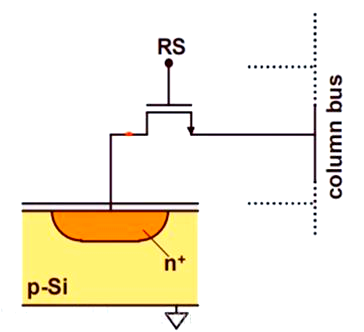

像素的种类繁多,其中PPS(无源像素传感器)是一种常见的类型。它包含一个PN结和行选择器,PN结即代表了像素的感光面积,具有高利用率的特点。然而,PPS也存在一定的局限,如噪声问题。这主要是由于PN结的电容较小,对电路噪声敏感,且其信号需先读出再放大,导致读出电路的噪声被一同放大。

PPS的读出过程包括复位、曝光、读出和循环四个步骤。在复位阶段,行选择地址接通Vdd电压,打开行选择器晶体管,使PN结与列选择器导通。随后,列选择器接上高反偏电压,如3.3V,使PN结进入反偏耗尽状态。完成复位后,关闭行选择器晶体管,断开PN结与列选择器的连接。接着进入曝光阶段,光子激发出的电子-空穴对在PN结内电场的作用下分别流向n+端和p-substrate,导致PN结反偏电压下降。读出阶段则是通过测量PN结反偏电压与复位后反偏电压的差值来获取感光信号。最后,完成读出后会对PN结进行reset操作,为下一次曝光做准备。

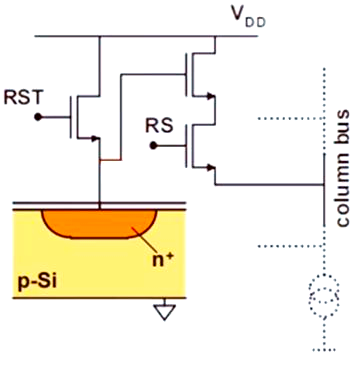

一个完整的3T有源像素单元包含PN结、行选择器RS、复位三极管RST以及源跟随器SF。其读出过程如下所述:

首先,打开RST三极管,为PN结施加反偏电压,进行复位操作。复位完成后,关闭RST。接着,光子进入PN结,产生电子-空穴对。在PN结内电场的作用下,电子流向n+端,而空穴则流向p-substrate,导致PN结反偏电压下降。曝光完成后,打开RS行选择器,PN结中的信号通过源跟随器SF放大后,被读出至column bus。此后,重复上述复位、曝光、读出的循环,以不断输出图像信号。

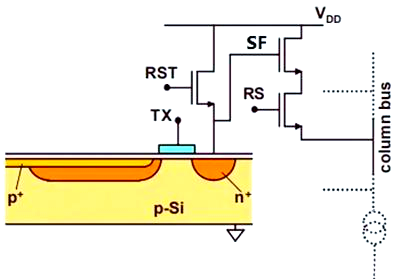

(3)4T APS

4T APS包含一个PPD(Pinned Photodiode)的感光区,以及四个晶体管TX、RST、RS和SF。PPD感光区采用PNP结构,有效降低了暗电流。其读出电路与光感区通过TX完全隔离,为引入信号处理电路(如CDS、DDS等)提供了便利。

读出过程如下所述:

曝光阶段,光照产生的电子-空穴对在PPD电场的作用下分离,电子流向n区,而空穴则流向p区。

复位阶段,曝光结束后,RST三极管打开,将读出区(n+区)复位至高电平,并读出复位电平至第一个电容。该电平包含了运放的offset噪声、1/f噪声以及复位引入的kTC噪声。

电荷转移阶段,TX三极管打开,将感光区内的电荷转移至n+区,这一机制类似于CCD中的电荷转移。

读出信号电平阶段,n+区的电压信号被读出至第二个电容,其中包含了光电转换产生的信号、运放offset、1/f噪声以及复位kTC噪声。

最终,通过将存储在两个电容中的信号相减(例如采用CDS技术),可以消除pixel中的主要噪声。经过模拟放大和ADC采样后,即可进行数字化信号输出。

4T APS的读出过程,通过一系列精心设计的阶段,实现了高效且低噪声的光电转换。在曝光阶段,PPD感光区利用其PNP结构,有效分离了由光照产生的电子-空穴对,确保电子和空穴能够分别流向n区和p区。随后,在复位阶段,RST三极管打开,将读出区复位至高电平,并读出包含各种噪声的复位电平至第一个电容。接着,电荷转移阶段开始,TX三极管打开,将感光区内的电荷转移至n+区,这一过程类似于CCD中的电荷转移机制。最后,在读出信号电平阶段,n+区的电压信号被读出至第二个电容,其中包含了光电转换产生的信号以及各种噪声。通过适当的信号处理技术,如CDS技术,可以有效地消除这些噪声,从而获得高质量的数字化信号输出。