SOI技术的定义

SOI(Silicon-On-Insulator)技术,是一种先进的半导体制造工艺。在这种工艺中,硅晶圆的一部分通过绝缘层(通常是二氧化硅)与基底硅层相隔离,从而显著减少了寄生电容和漏电流,进而提升了半导体器件的整体性能。

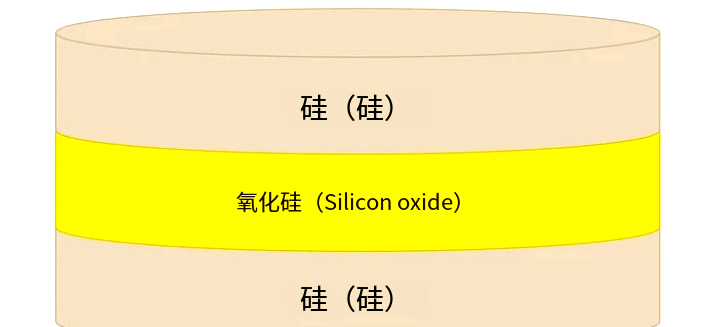

SOI晶圆的结构

SOI晶圆由三层关键部分组成:

- 顶层硅(Device Layer):这是最终形成各类半导体器件的硅层,其厚度根据应用需求而定,通常在几十纳米到几微米之间。

- 绝缘层(Buried Oxide, BOX):位于顶层硅与基底硅之间,是一层极薄的氧化硅(SiO₂)层,其厚度大约在几十到几百纳米范围内。这一层的主要作用是提供电气隔离,有效降低器件的寄生效应。

- 基底硅(Substrate):作为最底层,通常是一个厚度较大的硅基底,主要负责为整个晶圆提供机械支撑。

SOI技术的显著优势

与传统的体硅技术相比,SOI技术展现出了多项卓越的技术特性:

- 寄生电容的显著降低:SOI结构中,通过引入绝缘层(BOX),有效减少了器件与基底之间的寄生电容,从而提升了电路的开关速度,并降低了功耗。

- 漏电流的减少:绝缘层的引入不仅增强了电路的电气隔离,还显著减少了漏电流,特别是在低功耗应用场景下,这一优势更为明显。

- 抗辐射性能的提升:SOI器件对辐射的敏感度较低,这一特性使其非常适合航空航天以及其他高辐射环境的应用。

- 短沟道效应的改善:在深亚微米工艺中,SOI结构能够有效地抑制短沟道效应,确保器件性能的稳定性。

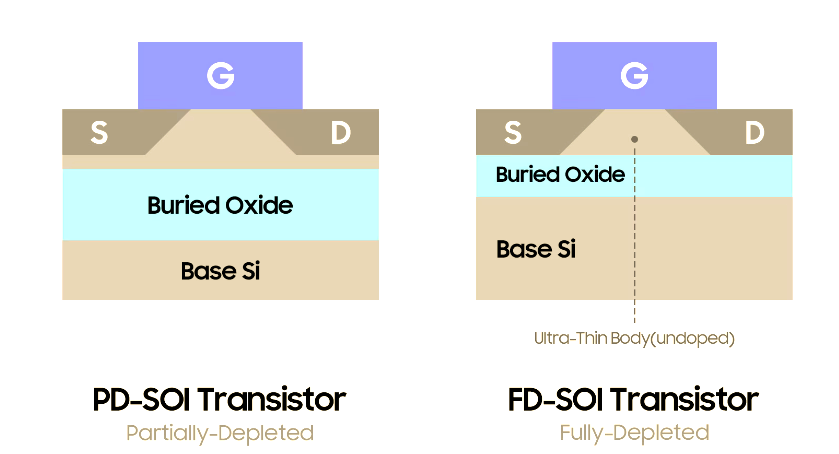

SOI器件的两种主要类型

完全耗尽型SOI(FD-SOI):此类SOI器件的顶层硅薄至可以完全耗尽,这一设计进一步降低了功耗并提升了器件的运行速度。

部分耗尽型SOI(PD-SOI):与FD-SOI不同,PD-SOI的顶层硅较厚,并未完全耗尽,因此仍存在一定的寄生效应。然而,由于其工艺难度相对较低,PD-SOI在特定应用场合下仍具有一定的适用性。

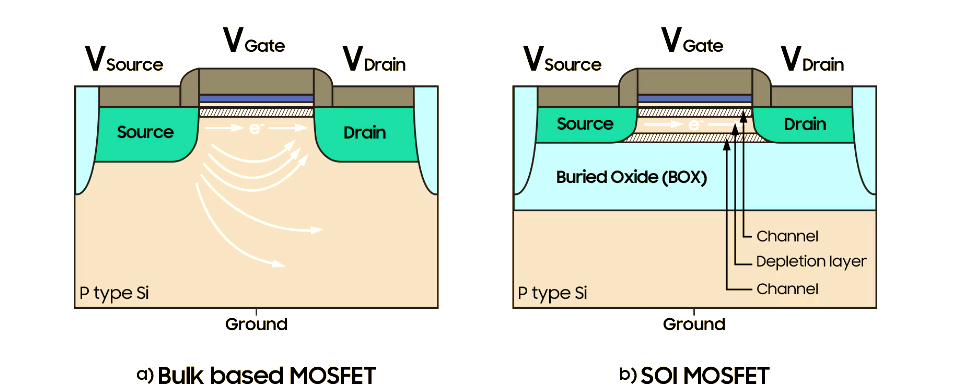

传统体硅(Bulk Silicon)技术的固有挑战

在传统的体硅工艺中,硅基底直接用作器件的核心材料。然而,随着半导体工艺尺寸的不断缩小,传统体硅技术逐渐面临一系列重大挑战:

寄生电容的增加:由于体硅器件与基底之间缺乏绝缘层,导致寄生电容显著增大,进而减慢开关速度并增加功耗。

短沟道效应的加剧:在特征尺寸不断缩小的趋势下,短沟道效应愈发显著,使得阈值电压变得不稳定,严重影响器件性能。

漏电流的激增:在超小尺寸的器件中,漏电流问题凸显,对功耗和可靠性构成严重威胁,特别是在追求低功耗的应用场景下。

热效应的困扰:体硅器件中的热传导路径较为复杂,容易导致局部热积累,从而对器件性能和稳定性造成不利影响。

SOI技术的优势与必要性

相较之下,SOI技术通过巧妙地在顶层硅与基底之间引入绝缘层(通常是二氧化硅),成功地克服了上述传统体硅技术的固有挑战。

SOI技术的优势与必要性

相较传统体硅技术,SOI技术凭借其独特结构,展现出了显著的优势。首先,通过在顶层硅与基底之间引入绝缘层,SOI技术有效减少了寄生电容,从而提升了开关速度和频率响应能力,这在高性能计算和通信领域尤为重要。其次,绝缘层的存在减轻了短沟道效应,保持了阈值电压的稳定性,提高了器件性能。此外,低漏电流特性使得SOI器件在低功耗应用中表现出色,如智能手机、可穿戴设备和物联网设备,延长了电池寿命并减少了热管理需求。同时,SOI器件对辐射环境的耐受性也更强,适用于航空航天、军事和高可靠性应用。最后,其优越的热管理能力使得在高密度集成电路中能够降低热积累对器件性能的影响。

SOI技术的应用

SOI技术已被广泛应用于多个领域,包括高性能微处理器、射频(RF)器件、低功耗消费电子产品和汽车电子等。在这些场景下,SOI技术的高开关速度、低功耗和高可靠性特性得到了充分利用。例如,高性能微处理器和服务器芯片需要快速响应和高吞吐量,而射频(RF)前端和高速通信芯片则要求严格的功耗控制和信号完整性。此外,航空航天和军事电子以及高可靠性汽车电子领域也充分利用了SOI技术的优势。

技术挑战与未来展望

尽管SOI技术具有诸多优势,但仍然面临一些技术挑战。其中之一是制造成本相对较高,这主要是由于薄膜厚度控制和应力管理等方面的复杂性。此外,SOI器件的热管理也不同于传统的体硅器件,需要特别的设计和考虑。然而,随着先进工艺的不断进步以及对高性能、低功耗需求的日益增长,SOI技术的前景依然十分广阔。未来的研究和发展将致力于降低成本、提高良率并进一步优化器件性能。

作者:胡工,拥有北京大学微电子学本科及硕士学位,现为北京大学半导体校友会成员。他在半导体行业深耕多年,目前常驻深圳。在此,他热切地期待与业界同仁交流与探讨,共同进步。在联系时,请务必注明您的姓名、所在公司及岗位,以便于我们更好地沟通。