重布线层(Re-distribution Layer,简称RDL)是芯片封装技术中的重要一环。它通过重新分布芯片上的电路连接,优化了电气性能并减小了封装尺寸。引线键合(Bond Wire)则是将芯片上的连接点与外部引脚相连接的工艺,确保了芯片的正常工作。倒片封装(Flip Chip Packaging)是一种先进的封装技术,其中芯片的触点直接与基板连接,提高了连接的可靠性和性能。异丙醇(Isopropyl Alcohol,简称IPA)在芯片封装过程中常被用作清洗剂,去除杂质和残留物,保证封装的纯净度。金属溅射(Metal Sputtering)是一种用于制备金属薄膜的工艺,它在晶圆级封装中发挥着关键作用。晶圆级封装(Wafer Level Packaging,简称WLP)是一种将封装工艺直接应用于晶圆级别的技术,大大提高了生产效率和封装密度。凸点下金属层(Under Bump Metallurgy,简称UBM)是封装工艺中的一层重要结构,它增强了凸点与基板的连接强度。裸片(Net Die)是指从晶圆上切割下来的芯片,是封装工艺的起点。扇出型封装(Fan-Out)和扇入型封装(Fan-In)是两种不同的封装方式,它们都采用了WLCSP(晶圆级芯片尺寸封装)技术,通过优化布局提高了封装的灵活性。

1 背景与发展

在芯片的设计与制造过程中,IO pad扮演着至关重要的角色。它不仅是芯片管脚信号处理的枢纽,还能将芯片内部的信号传递到管脚,反之亦然。然而,在传统的封装方式中,裸片的I/O触点往往仅限于芯片的边缘或周边,这在一定程度上限制了连接的密度和封装的灵活性。对于引线键合工艺而言,这种布局尚可应对,但当面临倒片封装等更先进的封装技术时,其局限性便逐渐显现。

1 传统晶圆封装的问题

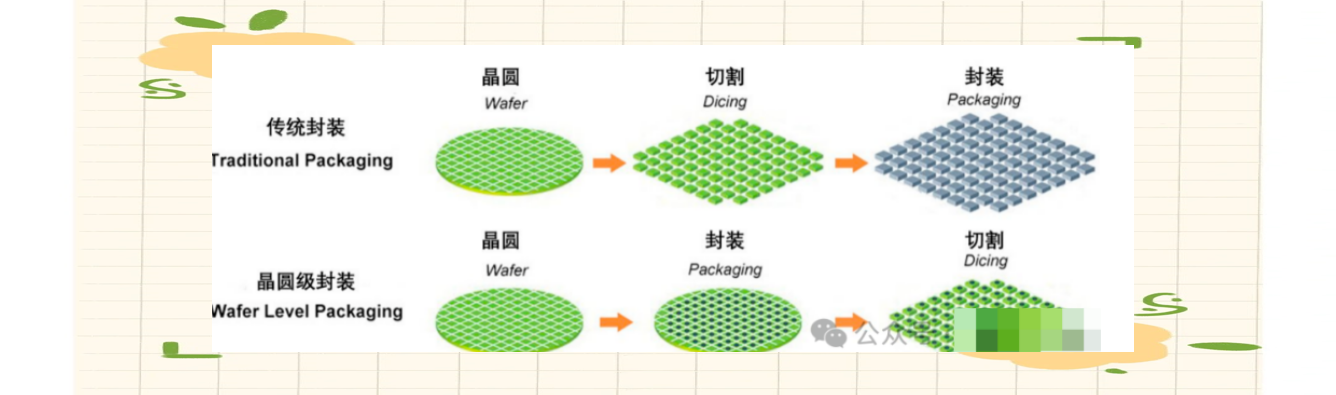

传统的晶圆封装方法将成品晶圆切割成单个芯片后,再进行黏合封装。这种方式的弊端在于封装与芯片制造流程的割裂,导致生产成本高昂,且需要引入引线框架、基板等介质,进一步降低了封装效率。

2 重布线层技术及其优势

重布线层技术通过在晶圆表面沉积金属层和介质层,并形成金属布线,从而在芯片上构建出一层金属线路网络。这一技术能够重新布局裸片的I/O端口,通过半导体工艺将触点延伸至芯片表面,并扩展至更为宽松的区域,实现面阵列排布。这使得封装过程中的触点连接不再局限于裸片的边缘,从而大大提高了连接密度、降低了封装难度,并提供了更为灵活的布线选项。此外,重布线层技术还能缩短信号传输路径、优化电热性能并抑制噪声,因此在高性能计算、通信设备等对热管理和信号完整性要求严格的应用中具有显著优势。

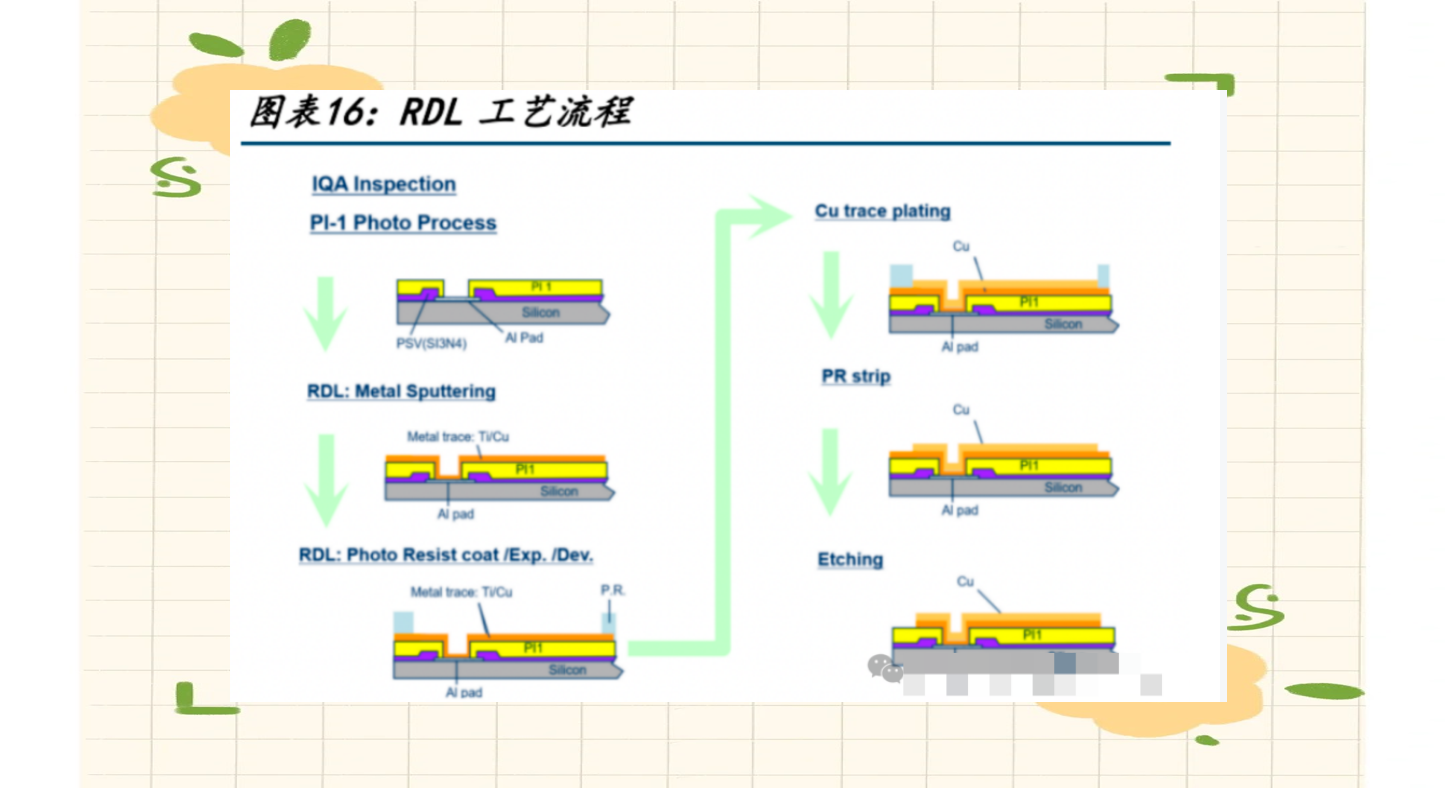

2 重布线层技术的具体步骤

重布线层(RDL)技术涉及到曝光、物理气象沉积(PVD)等关键步骤,其具体工艺流程如下所述:

形成绝缘层并开口,为后续步骤做准备。

通过旋涂膜技术涂覆并烘烤,以形成种子层。

涂抹光刻胶,经过曝光和显影后,形成所需的线路图案,并进行电镀铜垫。

去除多余的光刻胶,并进行刻蚀处理。

在完成第一层布线后,重复上述步骤,以开始构建第二层布线。

3 晶圆级封装(Wafer Level Packaging WLP)——扇入型封装和扇出型封装

在解决了连接问题之后,我们进一步探索了如何更好地进行封装。晶圆级封装,作为继贴片封装和刀片封装之后的又一重大技术突破,为我们提供了新的解决方案。它充分利用了重布线层技术的优势,使得在晶圆阶段就能对芯片进行统一布线,从而大大简化了封装流程。与传统的晶圆封装和倒片封装相比,晶圆级封装无需将成品晶圆切割成单个芯片后再进行封装,而是在晶圆上就直接完成了封装过程。这种创新使得芯片在成为最终产品之前就已经具备了半成品的形态,极大地提高了生产效率和降低了成本。

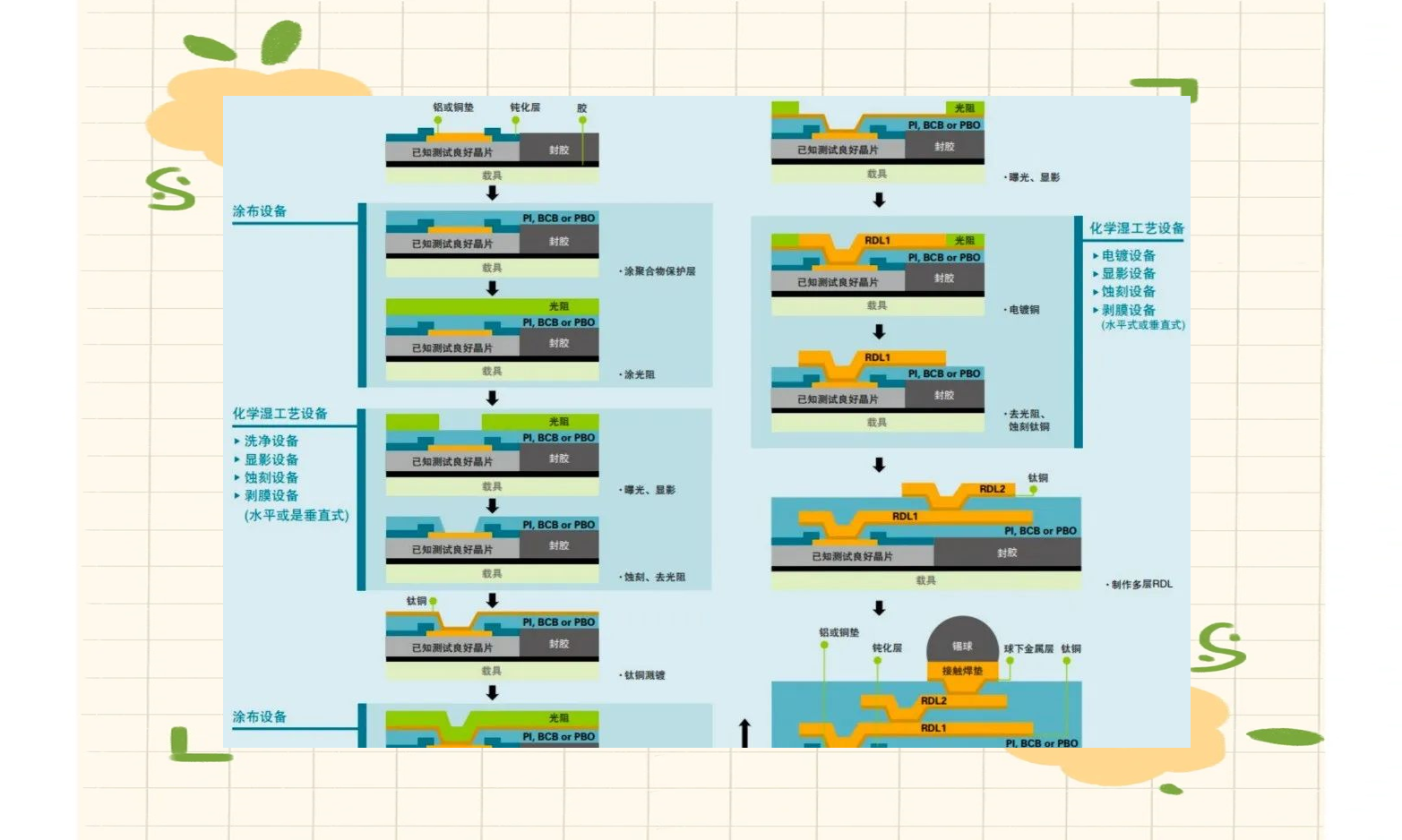

2 晶圆级封装的详细工艺流程

首先,为了增强芯片的钝化层并起到应力缓冲的作用,会在其上涂覆一层聚合物薄膜。可选的聚合物材料包括光敏聚酰亚胺(PI)、苯并环丁烯(BCB)以及聚苯并恶唑(PBO)。

接下来,通过重布线层(RDL)技术对芯片的铝/铜焊区进行重新布局,以确保新焊区满足对焊料球最小间距的要求,并按照阵列形式进行排布。在此过程中,光刻胶被用作选择性电镀的模板,以规划RDL的线路图形。随后,通过湿法蚀刻去除光刻胶和溅射层。

涂覆第二层聚合物薄膜的目的是使圆片表面平坦化并保护RDL层。在这层薄膜上,会通过光刻技术新开出焊区位置。

凸点下金属层(UBM)的制作工艺与RDL相似。完成后,通过掩膜板准确定位焊膏和焊料球,并将其放置于UBM上。随后,将整个结构放入回流炉中,使焊料经回流后与UBM形成良好的浸润结合,从而确保优质的焊接效果。

3 扇入型和扇出型封装

在晶圆级封装中,根据芯片尺寸的不同,我们可以将其分为扇入型WLCSP和扇出型WLCSP。其中,“扇”这一术语指的是芯片的尺寸大小。

1 扇入型(Fan-In)WLCSP

扇入型WLCSP的特点在于其封装布线、绝缘层以及锡球都直接位于晶圆的顶部。这种设计带来了以下优势:

- 尺寸优势:由于封装尺寸与芯片尺寸相一致,因此能够实现最小的尺寸封装。

- 电气性能优化:锡球直接与芯片相连,无需通过基板等媒介,从而缩短了电气传输路径,提升了电气性能。

- 成本效益:省去了基板和导线等封装材料,降低了工艺成本。特别是在晶圆上一次性完成封装的情况下,随着裸片数量的增多和生产效率的提高,成本节约效果更为显著。

然而,扇入型WLCSP也存在一定的不足:

- 物理和化学防护性能较弱:由于采用硅(Si)芯片作为封装外壳,其物理和化学防护性能相对较弱。

- 热膨胀系数差异:这些封装的热膨胀系数与其待固定的PCB基板存在显著差异,可能导致连接封装与PCB基板的锡球承受过大应力,从而影响焊点的可靠性。

2 扇出型(Fan-Out)WLCSP

扇出型WLCSP在继承了扇入型WLCSP的诸多优点的同时,还对其不足之处进行了有效改进。这种封装技术不仅具备尺寸优势、电气性能优化以及成本效益,还通过采用特定的封装外壳材料,显著提升了物理和化学防护性能。此外,它还解决了热膨胀系数差异的问题,从而确保了焊点的可靠性。

这个方案的精髓在于为每个芯片增添了一层额外的保护壳,这一改进基于扇入型WLCSP的基础设计。具体来说,它首先涉及将晶圆进行切割,随后将芯片按照晶圆的形状在载体上进行布局,并利用环氧树脂填充芯片间的空隙,从而为每个芯片构建起一层额外的保护。接下来的流程与扇入型WLCSP相似,采用重布线层技术对每个芯片进行处理。最终,通过切割得到成品芯片。

从图示中可以清晰看出,扇出型WLCSP相较于扇入型,在外部增加了一圈环氧树脂保护壳。由于面积的增大,重布线层技术为扇出型提供了更多的I/O触点,进而提升了连接的密度。值得注意的是,扇入型WLCSP的封装锡球仅限于芯片表面,而扇出型WLCSP的封装锡球可以扩展至芯片外部,这一设计进一步优化了其电气性能。

2 总结

解决连接问题

高传输速度:相较于传统金属引线产品,WLP因其较短的连接线路而在高频环境下展现出优越性能。

高密度连接:WLP采用数组式连接方式,突破了芯片四周的限制,从而大幅提高了单位面积内的连接密度。

解决封装问题

封装尺寸小:WLP避免了引线、键合和塑胶工艺,使得封装后的芯片尺寸与原始裸片保持一致,达到了最小的封装尺寸。

缩短生产周期:WLP的生产流程经过优化,从芯片制造到封装成品的整个过程中,中间环节显著减少,从而提高了生产效率,缩短了生产周期。

降低工艺成本:WLP在硅片层面完成封装测试,通过大规模生产实现成本最小化。随着芯片设计尺寸的减小和硅片尺寸的增大,单个器件的封装成本也在相应降低。同时,WLP还能充分利用晶圆制造设备,进一步降低了生产设施费用。