工艺微缩是集成电路制造技术发展的重要特征之一。工艺微缩表现为随着工艺能力的提高,可以加工出更小尺度的器件,这也意味着在相同面积的芯片上可以集成更多的器件。集成电路中的有源区、栅、接触孔、金属互连线等关键部位的大小和间距等关键参数称为特征尺寸,具备某一系列特征尺寸称为技术节点。

集成电路的发展历程

随着芯片不断向微型化发展,特征尺寸不断缩小,从而使集成电路产业发展进入了后摩尔时代,其发展周期开始放缓,从2年一个周期迈向3年一个周期。在封装观念上也发生了革命性变化,从原来的封装元件概念演变成封装系统,包括 SoC(System On Chip)、SiP(System In Packet)等。

SiP模组是一个功能齐全的子系统,它将一个或多个IC芯片及被动元件整合在一个封装中。此IC芯片(采用不同的技术:CMOS、BiCMOS、GaAs等)是Wire bonding芯片或Flipchip芯片,贴装在Leadfream、Substrate或LTCC基板上。被动元器件如RLC、Balun及滤波器(SAW/BAW等)以分离式被动元件、整合性被动元件或嵌入式被动元件的方式整合在一个模组中。与SoC相比,SiP具有开发周期短,成本低,灵活度高等优势,这意味着多芯片系统级封装(SiP)市场增长。按照芯片组装方式的不同,SiP可以分为2D、2.5D、3D结构。

l 2D、2.5D封装结构

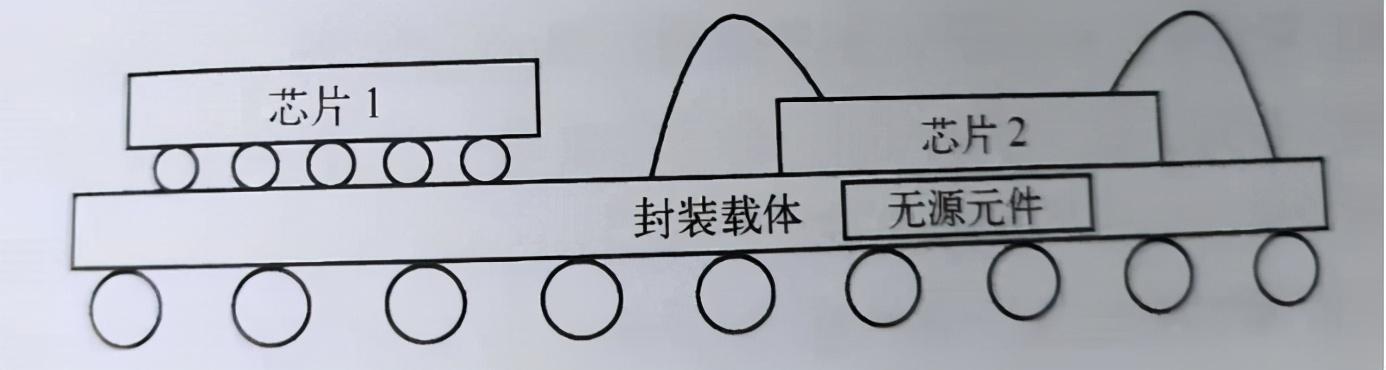

2D结构SiP是将多个芯片组装到同一封装载体表面,组装工艺有引线键合(WB)、倒装芯片(FC),或者两种工艺混合使用,由于封装载体上的布线比芯片上的布线宽出3个数量级,所以该结构在互连芯片的数量上会受到一定的限制。

2D结构的SiP

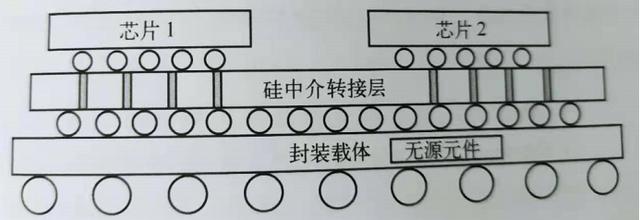

2.5D封装是在2D封装结构的基础上,在芯片和封装载体之间加入了一个硅中介转接层,该中介转接层上利用硅通孔(Through Silicon Via, TSV)连接其上、下表面的金属,多采用倒装芯片组装工艺。由于采用了中介转接层,其表面金属层的布线可以使用与芯片表面布线相同的工艺,使产品在容量及性能上比2D结构得到巨大提升。

2.5D结构的SiP

l 3D封装结构

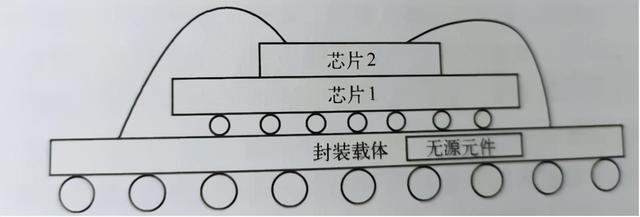

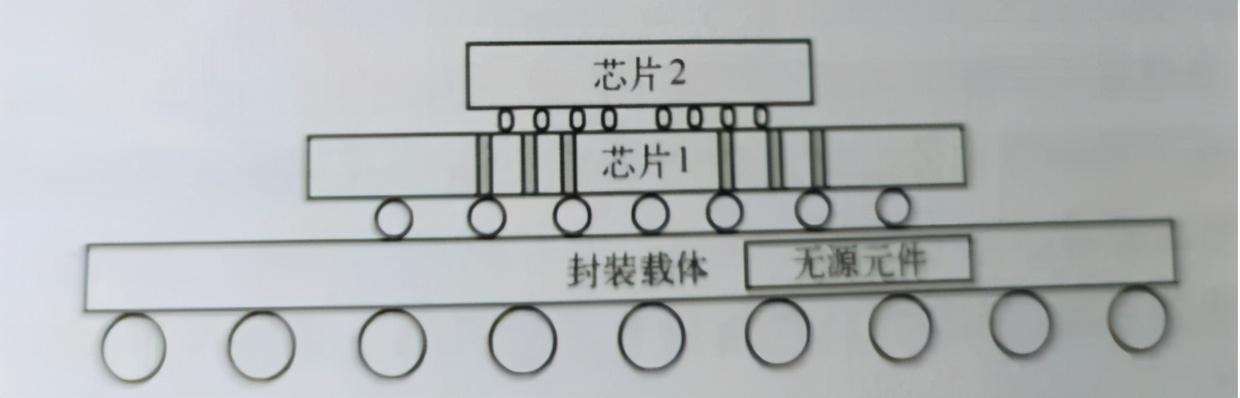

3D结构是将芯片与芯片直接堆叠,可采用引线键合、倒装芯片或二者混合的组装工艺,也可采用硅通孔技术进行互连。3D结构进一步缩小了产品尺寸,提高了产品容量和性能。目前,散热较差、成本较高是制约TSV技术发展的主要因素。

3D结构的SiP(引线键合和倒装芯片)

3D结构的SiP(硅通孔和倒装芯片)

l 堆叠封装(PoP)结构

PoP(PackageonPackage,堆叠封装)是一种将分离的逻辑和存储BGA在垂直方向上结合起来的封装技术。在这种结构中,两层以上的封装单元自下而上堆叠在一起,中间留有介质层来传输信号。PoP技术增大了器件的集成密度,底层的封装单元直接与PCB板接触。传统的PoP是基于基板的堆叠,随着存储器对高带宽的需求,球间间隔要求更小,未来将会与FOWLP技术相结合,做基于芯片的堆叠。

小结

SIP的特点在于把多个半导体芯片和无源器件封装在同一个芯片内,组成一个系统级的芯片,而不再用PCB板来作为承载芯片连接之间的载体,可以解决因为PCB自身的先天不足带来系统性能遇到瓶颈的问题。以处理器和存储芯片举例,因为系统级封装内部走线的密度可以远高于PCB走线密度,从而解决PCB线宽带来的系统瓶颈。举例而言,因为存储器芯片和处理器芯片可以通过穿孔的方式连接在一起,不再受PCB线宽的限制,从而可以实现数据带宽在接口带宽上的提升。

近年来,SiP模块凭借降低成本、提升效率、简化制造流程等特点,应用领域已从智能手机、可穿戴设备、物联网等依赖技术更迭的终端市场渗透拓展至工业控制、 智能汽车、云计算、医疗电子等诸多新兴领域,逐步打开了市场空间。SIP技术满足了当今电子产品更轻、更小和更薄的发展需求,在微电子领域具有广阔的应用市场和发展前景。此外,国际上至今尚没有制定出SIP技术的统一标准,在一定程度妨碍了SIP技术的推广应用。由此可见,未来SIP技术的发展还面临着一系列的问题和挑战,有待于软件、IC、封装、材料和设备等专业厂家密切合作,共同发展和提升SIP技术。